Going green is becoming table stakes no matter the sector, and the semiconductor industry formalized a commitment to sustainability by launching the Semiconductor Climate Consortium (SCC).

Going green is becoming table stakes no matter the sector, and the semiconductor industry formalized a commitment to sustainability by launching the Semiconductor Climate Consortium (SCC).

Fan-out wafer-level packaging (FOWLP) is a key enabler in the industry shift from transistor scaling to system scaling and integration. The design fans out the chip interconnects through a redistribution layer instead of a substrate. Compared to flip-chip ball grid array (FCBGA) or wire bonds, it creates lower thermal resistance, a slimmer package, and potentially lower costs.

When transistors can’t get any smaller, the only direction is up.

The U.S. CHIPS and Science Act spurred a rush to build new semiconductor fabs in the United States. So far, there are at least nine new fabs planned or under construction, as well as expansion plans at many existing fabs. One challenge the industry faces is matching a huge influx of fab capacity worldwide with the notorious boom-bust cycles of the semiconductor industry. But there may be another challenge looming: having enough skilled labor to operate and support these fabs.

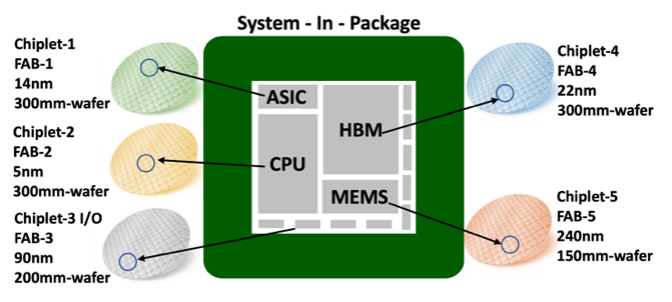

ECE Assistant Professor Farimah Farahmandi has received funding from the Office of Naval Research (ONR) in support of her three-year project, “SVH: Security Verification of Heterogenous Integration.” The $510k grant supports work which aims to develop novel security verification techniques to check against integration and lifecycle threats that impact the confidentiality, integrity, and availability of heterogenously integrated devices, commonly known as ‘Systems-in-Package’ (SiP).

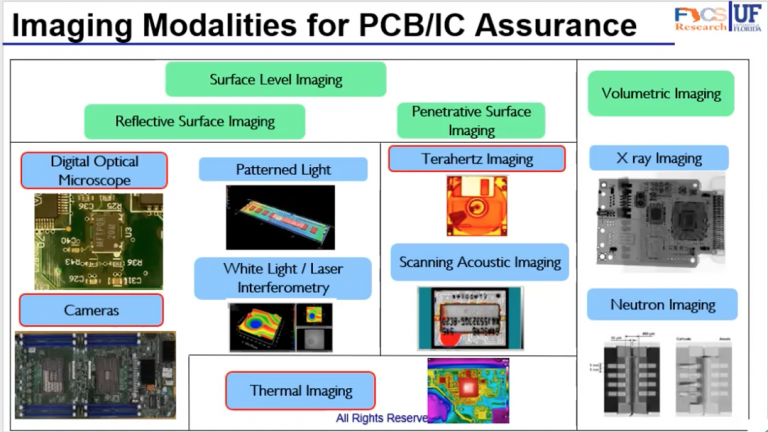

ECE Assistant Professor Navid Asadi reminds us of another issue with modern chips—physical assurance. Put another way, how can we be sure that the chips inside our devices are safe, reliable, and will perform as they were designed? As the bulk of chips are fabricated outside the purview of the U.S., these questions are even more critical in a national security sense.